SDRAM

SDRAM (англ. Synchronous Dynamic Random Access Memory — синхронная динамическая память с произвольным доступом) — тип запоминающего устройства, использующегося в компьютере в качестве ОЗУ.

В отличие от других типов DRAM, использовавших асинхронный обмен данными, ответ на поступивший в устройство управляющий сигнал возвращается не сразу, а лишь при получении следующего тактового сигнала. Тактовые сигналы позволяют организовать работу SDRAM в виде конечного автомата, исполняющего входящие команды. При этом входящие команды могут поступать в виде непрерывного потока, не дожидаясь, пока будет завершено выполнение предыдущих инструкций (конвейерная обработка): сразу после команды записи может поступить следующая команда, не ожидая, когда данные окажутся записаны. Поступление команды чтения приведёт к тому, что на выходе данные появятся спустя некоторое количество тактов — это время называется задержкой (англ. SDRAM latency) и является одной из важных характеристик данного типа устройств.

Циклы обновления выполняются сразу для целой строки, в отличие от предыдущих типов DRAM, обновлявших данные по внутреннему счётчику, используя способ обновления по команде CAS перед RAS.

История использования

Массовый выпуск SDRAM начался в 1993 году. Первоначально этот тип памяти предлагался в качестве альтернативы для дорогой видеопамяти (VRAM), однако вскоре SDRAM завоевал популярность и стал применяться в качестве ОЗУ, постепенно вытесняя другие типы динамической памяти. Последовавшие затем технологии DDR позволили сделать SDRAM ещё эффективнее. За разработкой DDR SDRAM, последовал стандарт DDR2 SDRAM, а затем и DDR3 SDRAM.

SDR SDRAM

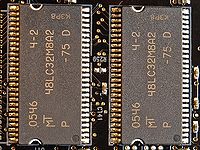

Первый стандарт SDRAM с появлением последующих стандартов стал именоваться SDR (Single Data Rate — в отличие от Double Data Rate). За один такт принималась одна управляющая команда и передавалось одно слово данных. Типичными тактовыми частотами были 66, 100 и 133 МГц. Микросхемы SDRAM выпускались с шинами данных различной ширины (обычно 4, 8 или 16 бит), но как правило, эти микросхемы входили в состав 168-пинного модуля DIMM, который позволял прочитать или записать 64 бита (в варианте без контроля чётности) или 72 бита (с контролем чётности) за один такт.

Использование шины данных в SDRAM оказалось осложнено задержкой в 2 или 3 такта между подачей сигнала чтения и появлением данных на шине данных, тогда как во время записи никакой задержки быть не должно. Потребовалась разработка достаточно сложного контроллера, который не позволял бы использовать шину данных для записи и для чтения в один и тот же момент времени.